# Classical and Modern Control Design: with examples from power electronics

### Richard Tymerski

Portland State University

Department of Electrical and Computer Engineering

Portland, Oregon, USA

### Frank Rytkonen

Oregon Institute of Technology Department of Electrical Engineering and Renewable Energy Wilsonville, Oregon, USA

# ${\bf Acknowledgements}$

The authors would like to express their sincere gratitude to a number of former students who have greatly contributed to making this book possible. Of particular note, Clint Lieser and Andrew Chuinard ... (To be expounded upon.)

# Preface

This is the preface.

# Contents

|   | Ack:<br>Pref | nowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ii<br>iii |

|---|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Ι | Cl           | assical Control: Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1         |

| 1 |              | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3         |

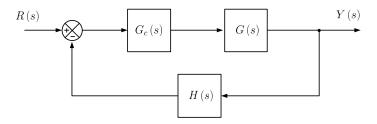

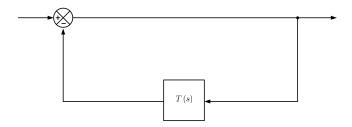

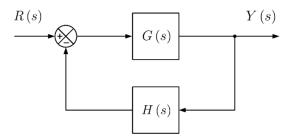

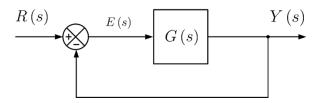

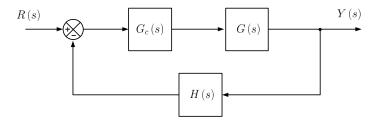

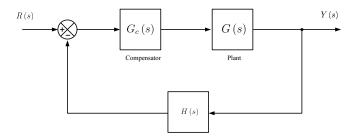

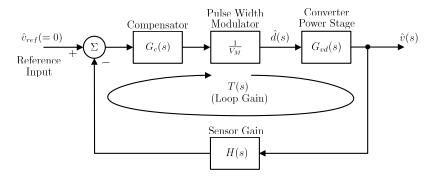

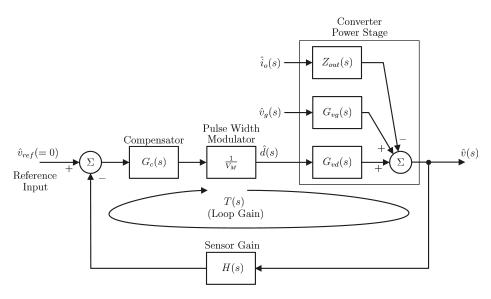

|   | 1.1          | Basic Feedback Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3         |

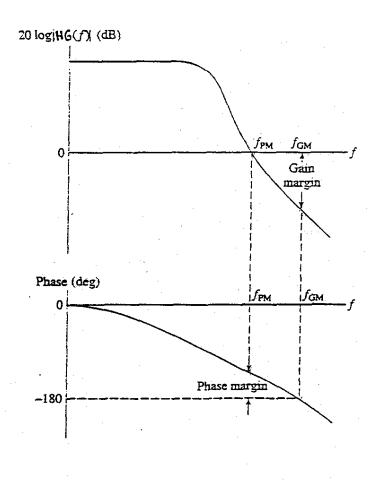

|   | 1.2          | Stability - Absolute and Relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4         |

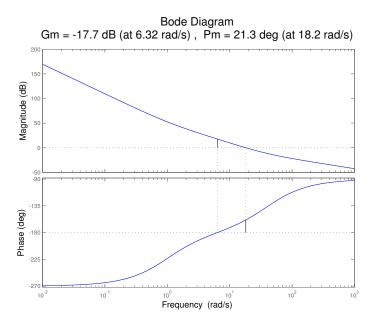

|   | 1.3          | Stability Analysis Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8         |

|   |              | 1.3.1 Matlab Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14        |

| 2 | Svs          | tem Stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15        |

| _ | 2.1          | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15        |

|   | 2.2          | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15        |

|   |              | J J J I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16        |

|   |              | J J J I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16        |

|   | 2.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17        |

|   |              | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20        |

|   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20        |

|   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21        |

| _ | <b>a</b> .   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| 3 |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23        |

|   | 3.1          | , 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25        |

|   | 0.0          | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31        |

|   | 3.2          | o de la companya de l | 33        |

|   |              | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36        |

|   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41        |

|   |              | 9-2-9 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43        |

|   |              | 9:2·2 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46        |

|   |              | 5-2-0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49        |

|   |              | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51        |

|   |              | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53        |

|   | 3.3          | Note: partial fraction containing a complex pole pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58        |

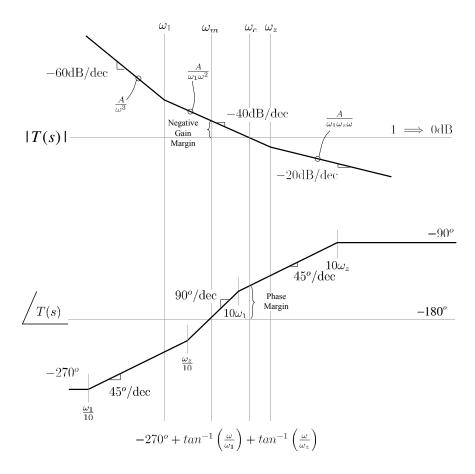

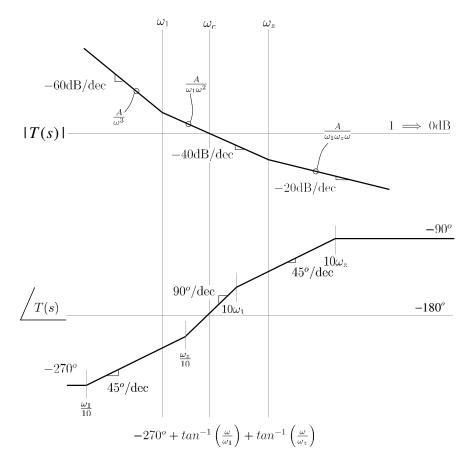

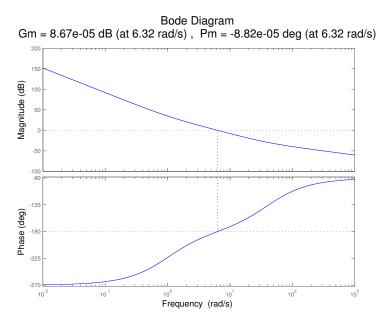

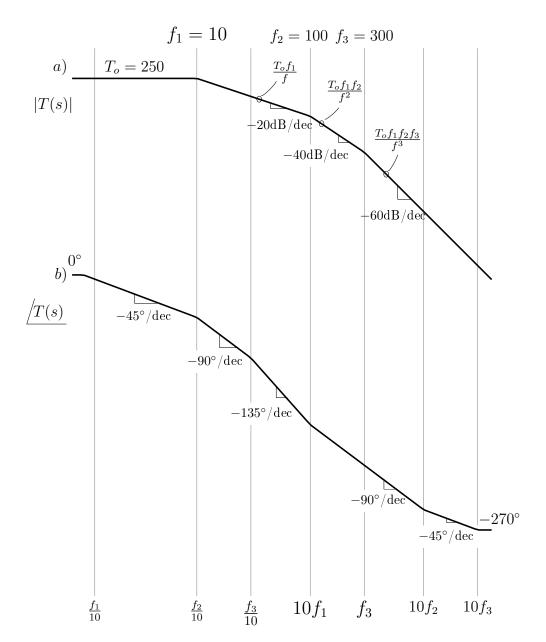

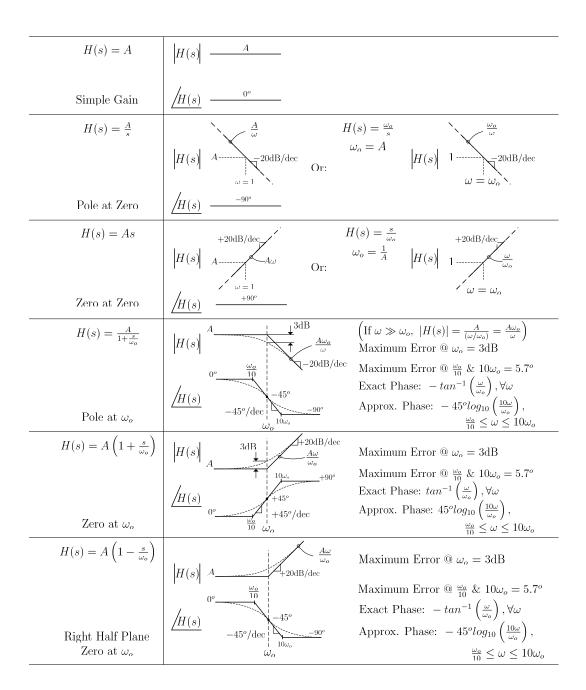

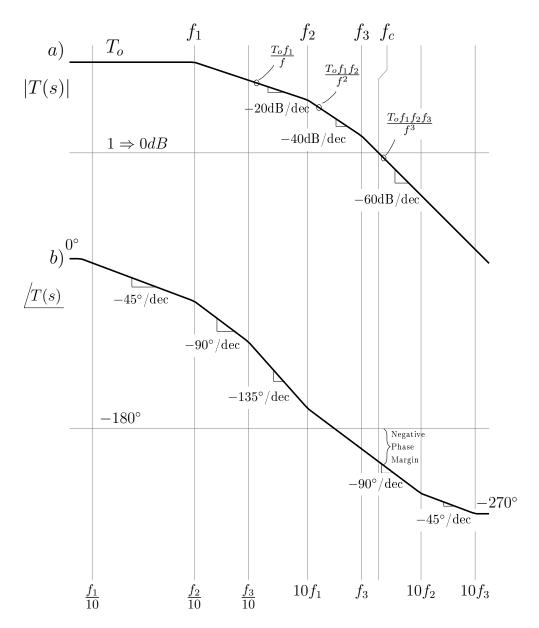

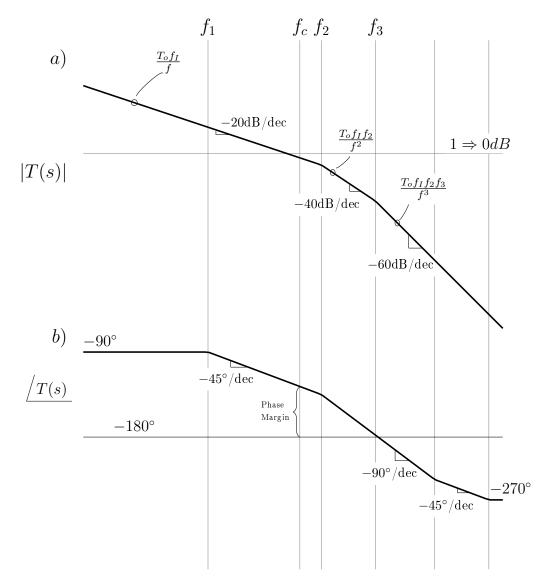

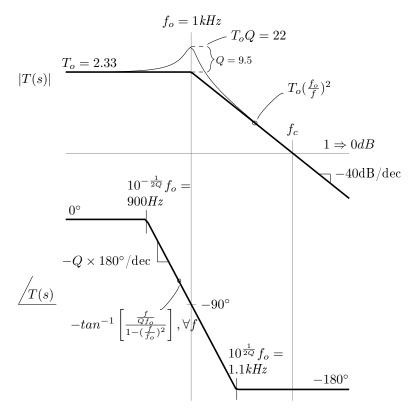

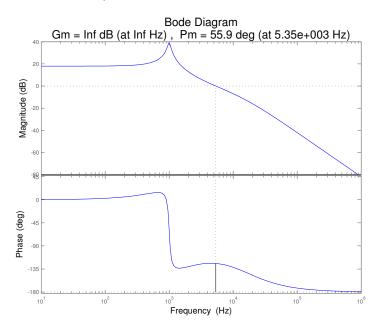

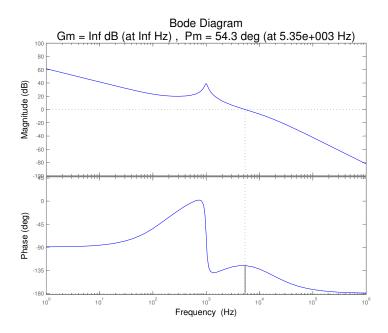

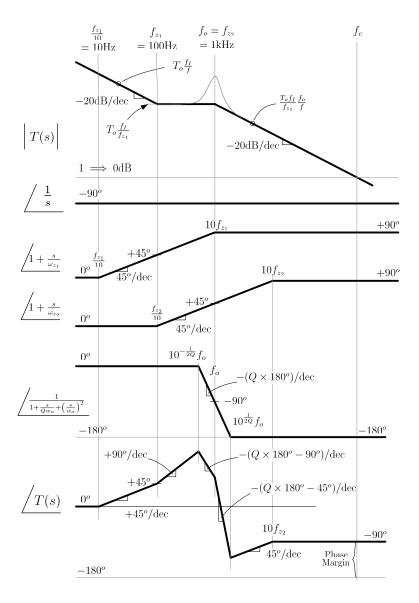

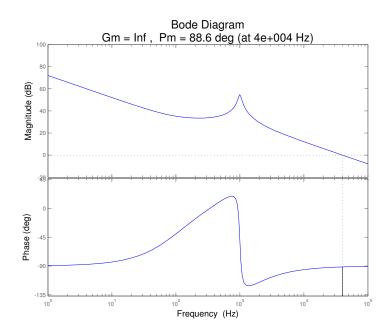

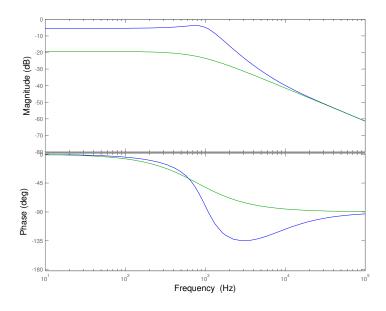

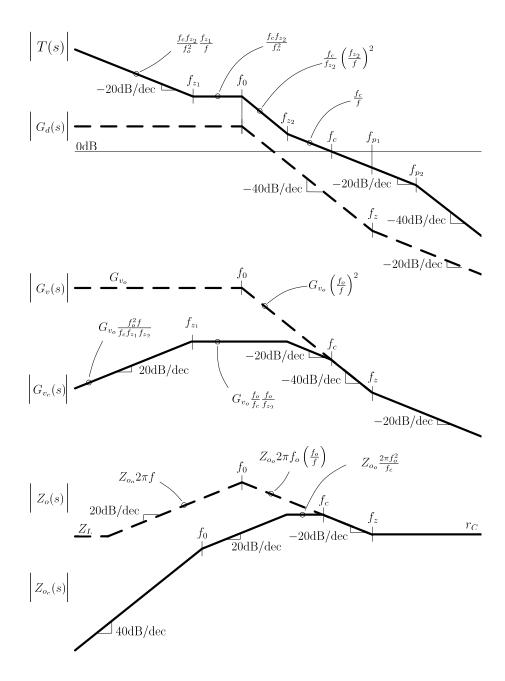

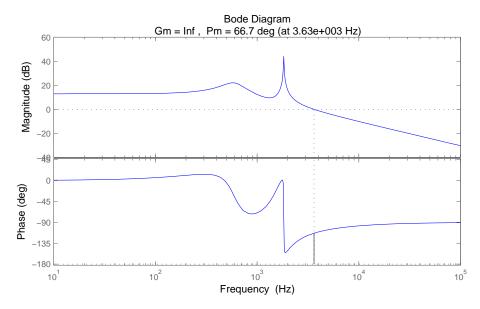

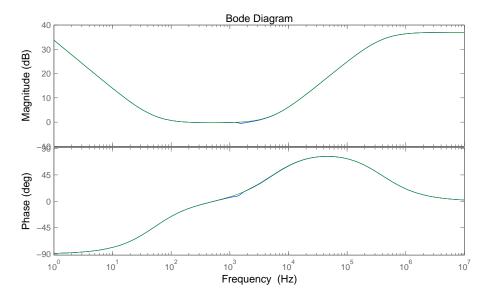

| 4 | Bod  | le Plots                                                   | 59  |

|---|------|------------------------------------------------------------|-----|

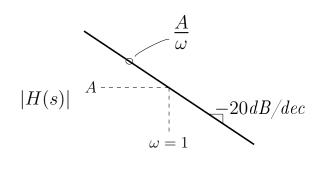

|   | 4.1  | Simple Gain                                                | 59  |

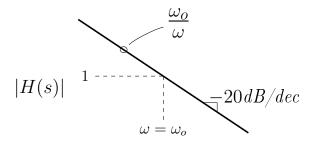

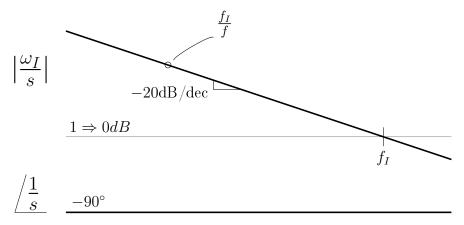

|   | 4.2  | Pole at Zero                                               | 60  |

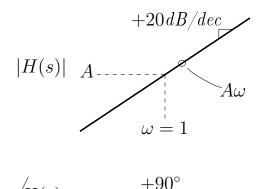

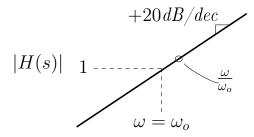

|   | 4.3  | Zero at Zero                                               | 61  |

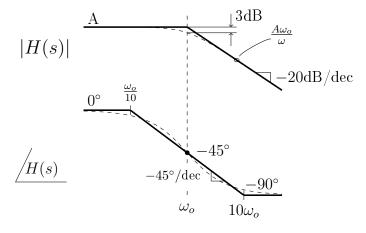

|   | 4.4  | Pole at $\omega_o$                                         | 62  |

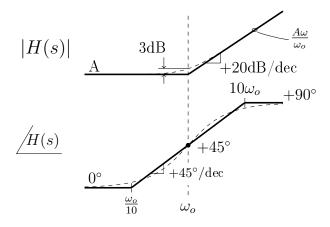

|   | 4.5  | Zero at $\omega_o$                                         | 63  |

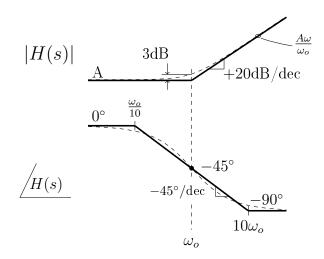

|   | 4.6  | Right Half Plane Zero at $\omega_o$                        | 63  |

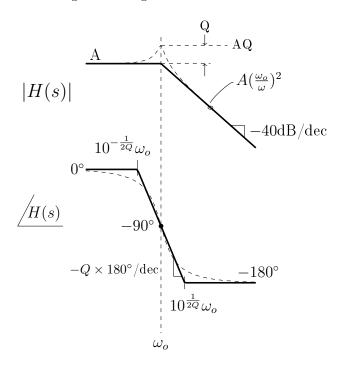

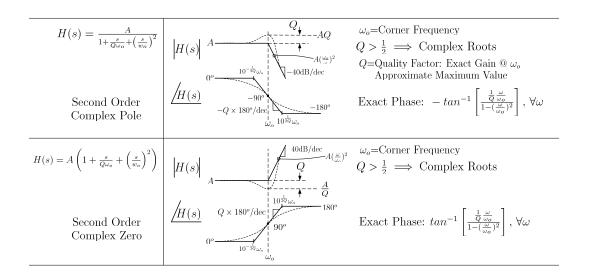

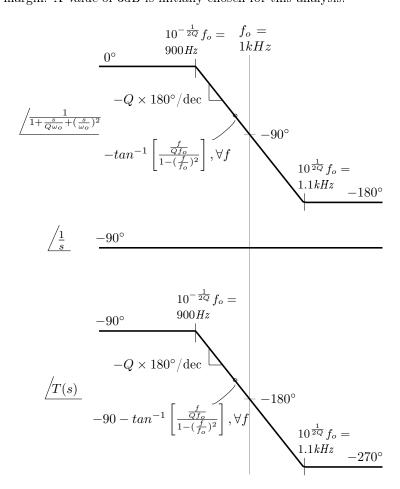

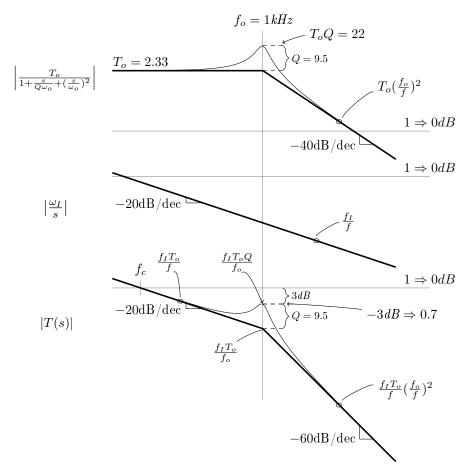

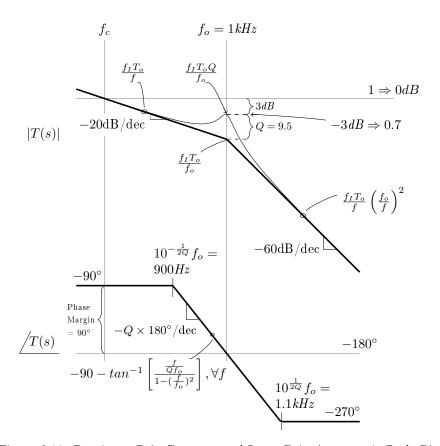

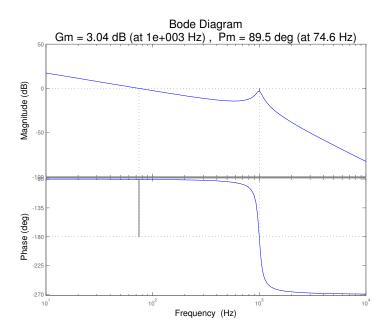

|   | 4.7  | Complex Pole Pair with Resonant Frequency at $\omega_o$    | 63  |

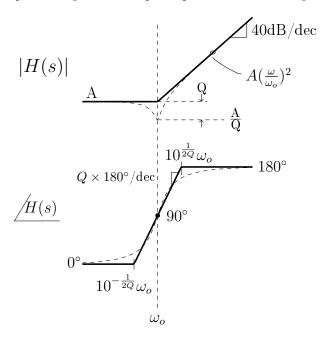

|   | 4.8  | Complex Zero Pair with Resonant Frequency at $\omega_o$    | 64  |

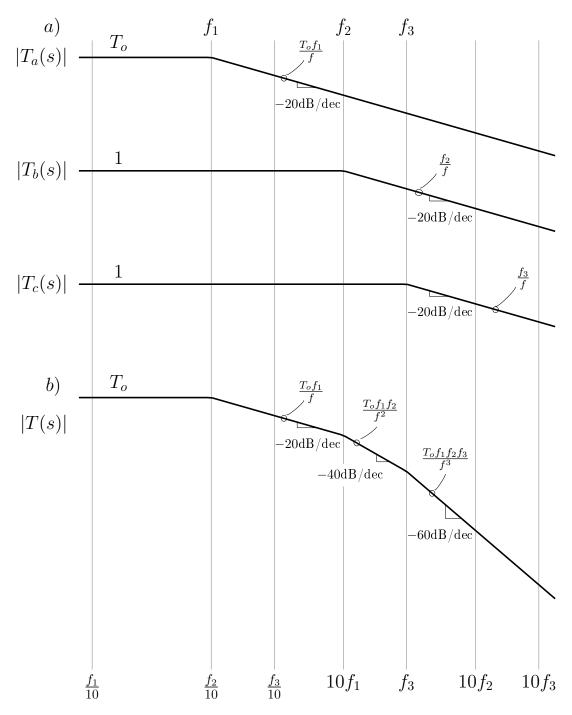

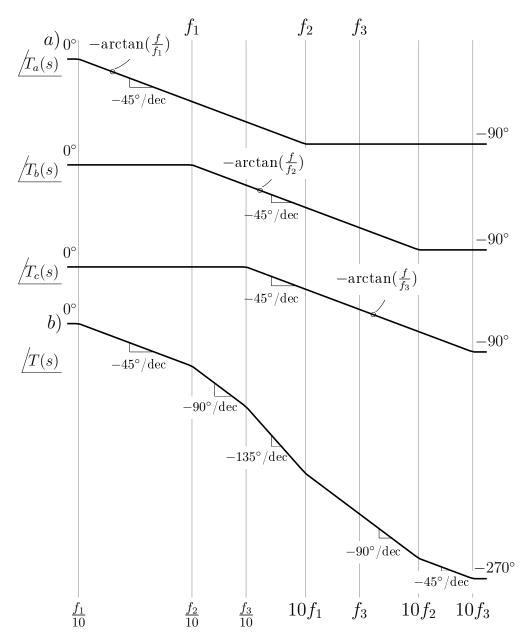

|   | 4.9  | Composite Transfer Functions                               | 65  |

|   | 4.10 | Summary of Bode Plots                                      | 70  |

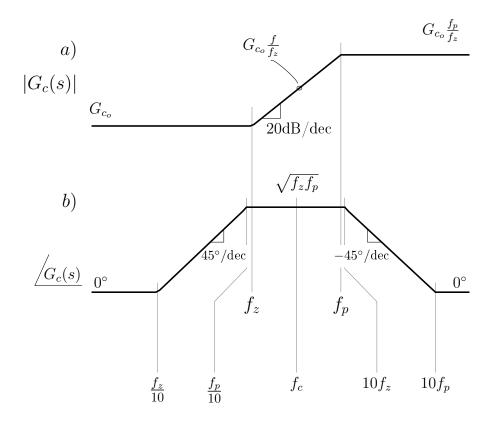

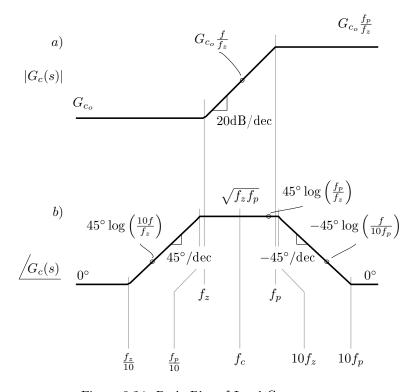

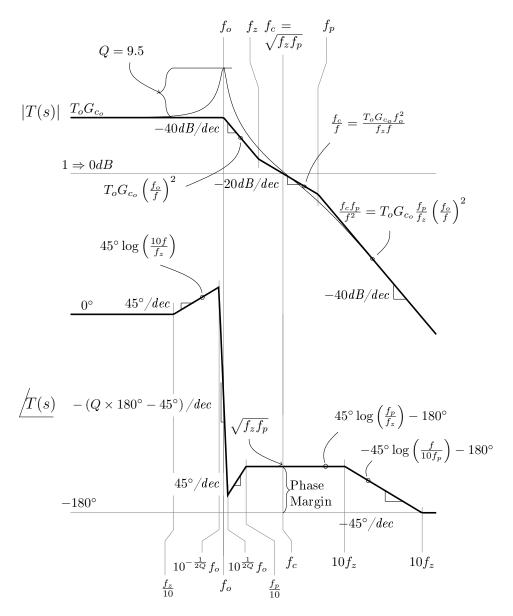

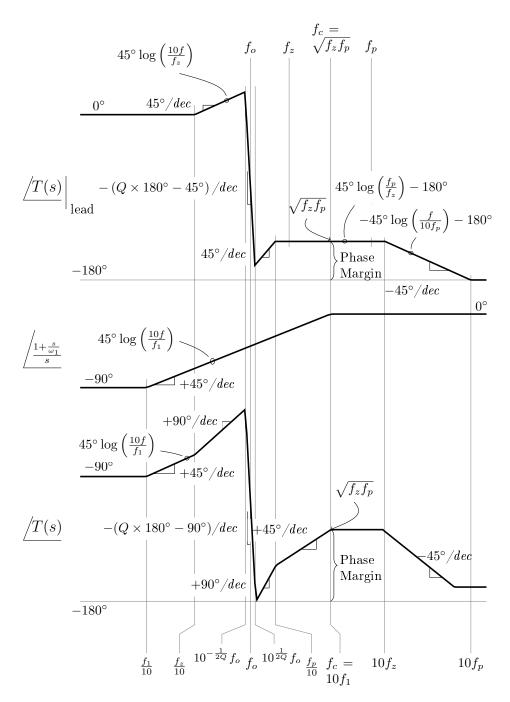

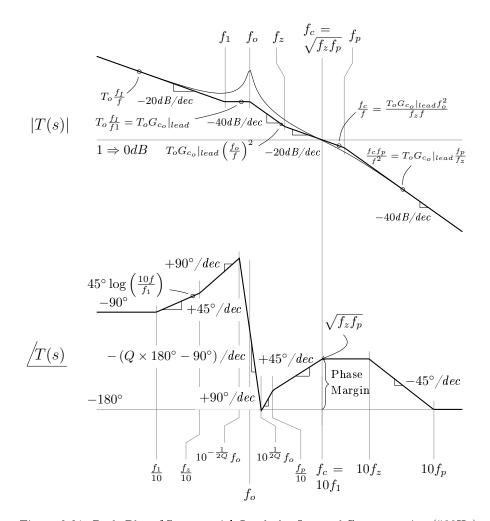

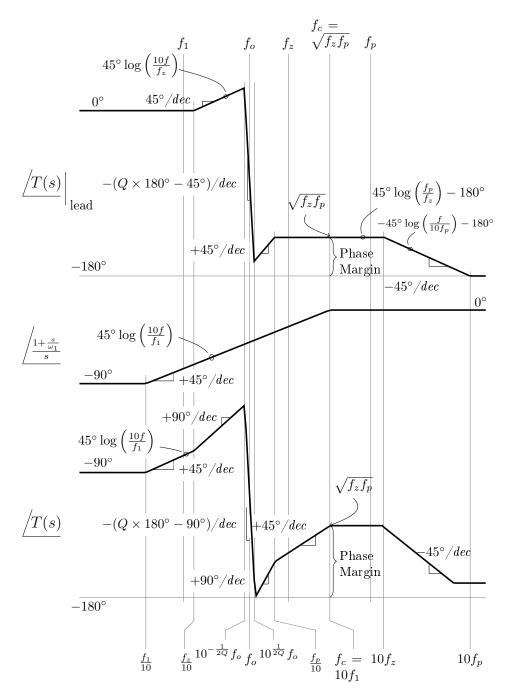

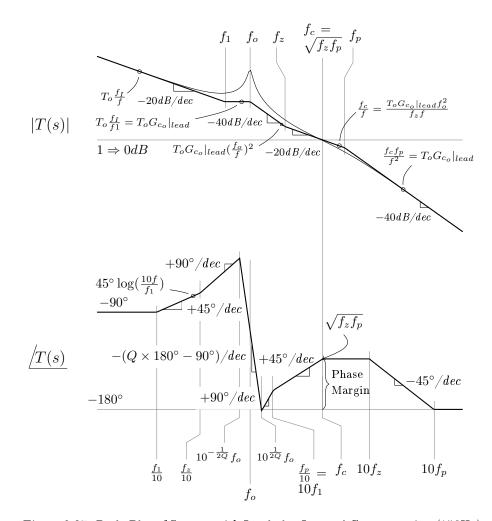

| 5 | Con  | npensator Design                                           | 73  |

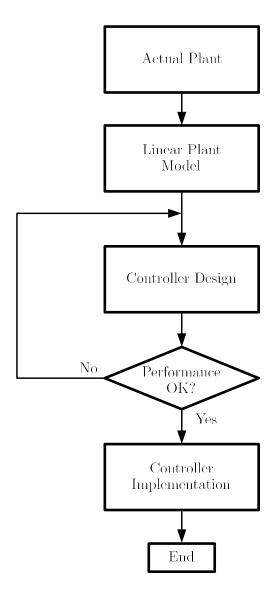

|   | 5.1  | Design Procedure                                           | 73  |

|   |      | 5.1.1 Introduction                                         | 73  |

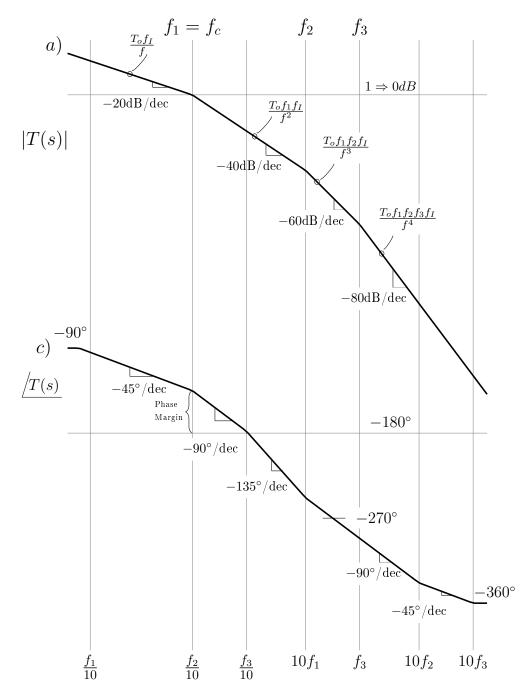

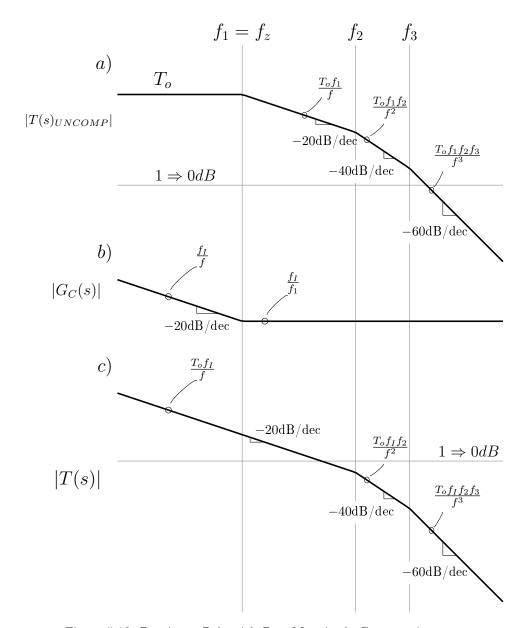

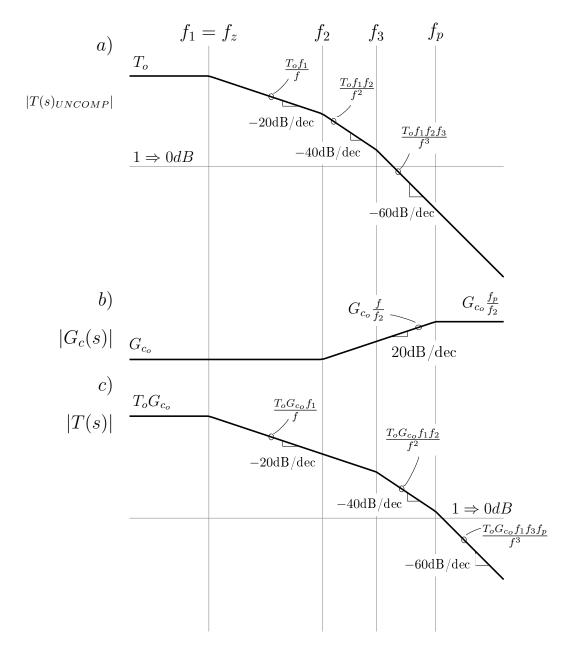

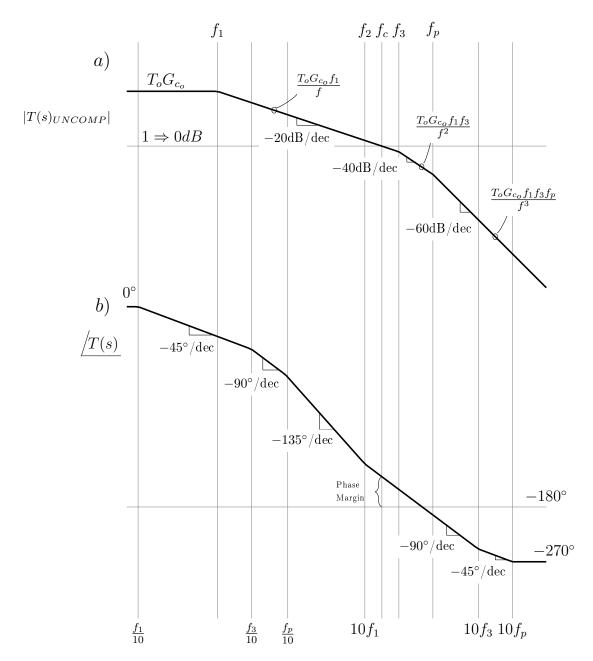

|   |      | 5.1.2 Uncompensated System                                 | 74  |

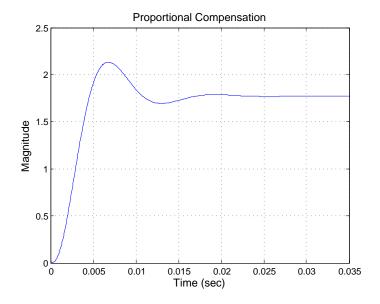

|   |      | 5.1.3 Proportional Compensated System                      | 78  |

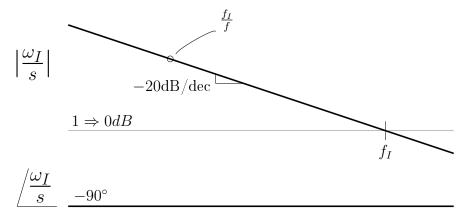

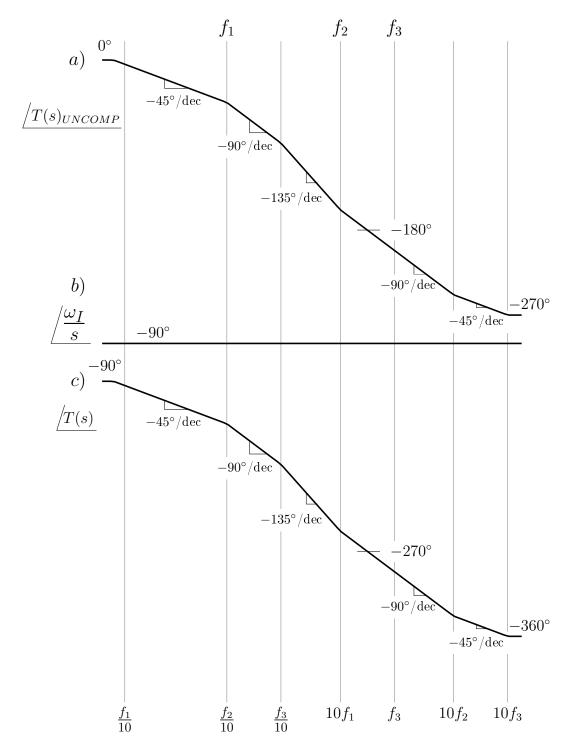

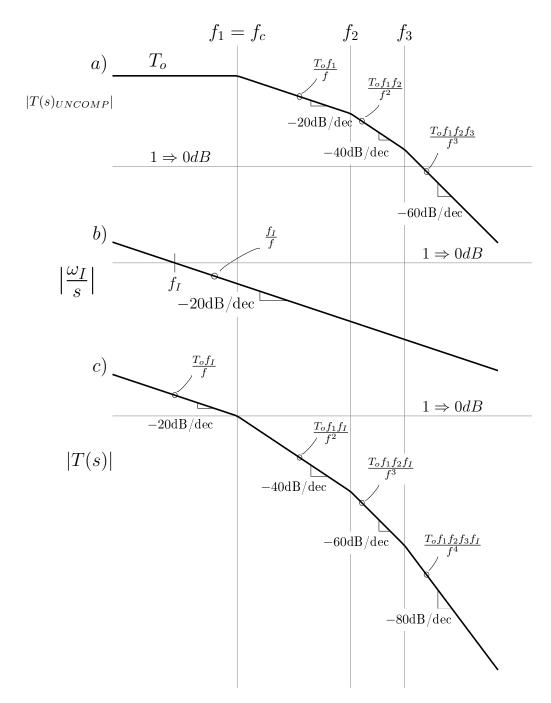

|   |      | 5.1.4 Dominant Pole Compensated System                     | 80  |

|   |      | 5.1.5 Dominant Pole Compensated System with zero           | 82  |

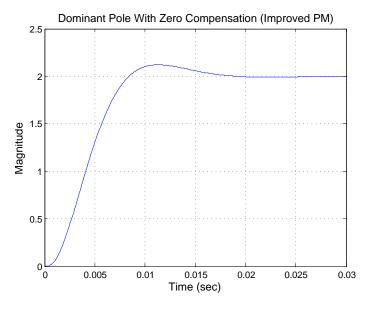

|   |      | 5.1.6 Dominant Pole Compensated System with zero, improved |     |

|   |      | phase margin                                               | 84  |

|   |      | 5.1.7 Lead Compensated System                              | 85  |

|   |      | 5.1.8 Lead Compensated System with integrator and zero     | 87  |

|   |      | 5.1.9 Summary                                              | 88  |

|   |      | 5.1.10 MATLAB Code                                         | 103 |

|   |      |                                                            |     |

| Η | С    | lassical Control: Application 1                            | 109 |

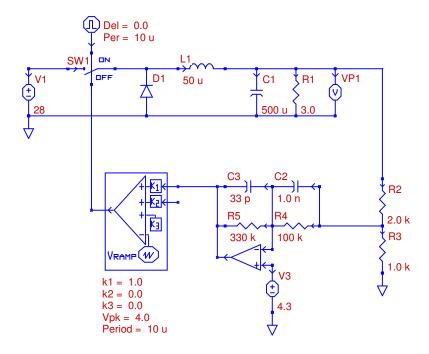

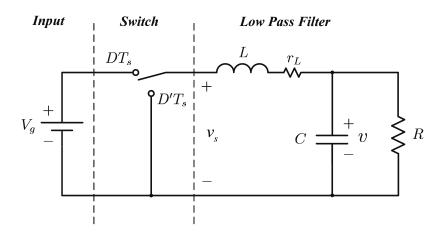

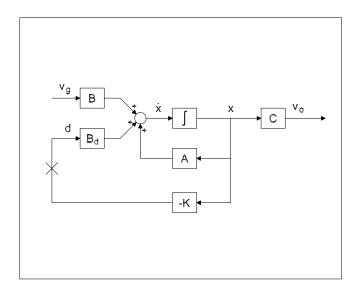

| 6 | Mod  | delling - Introduction                                     | 111 |

|   | 6.1  | Introduction                                               | 111 |

| - | mı.  |                                                            | 110 |

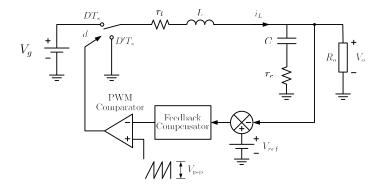

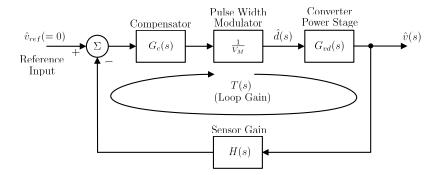

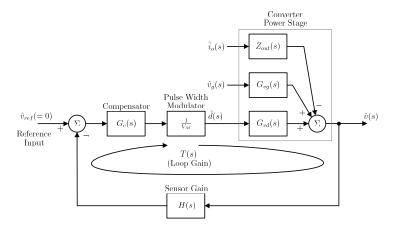

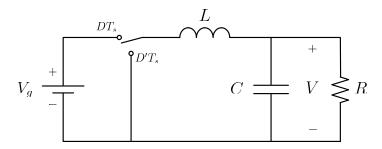

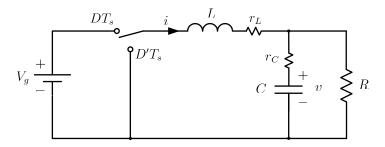

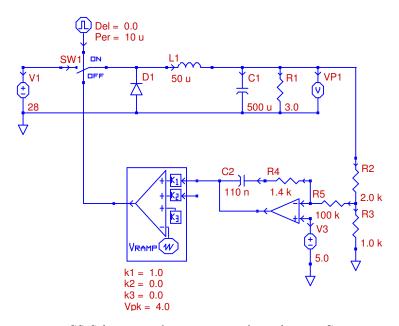

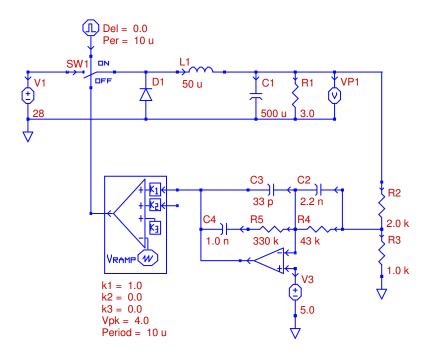

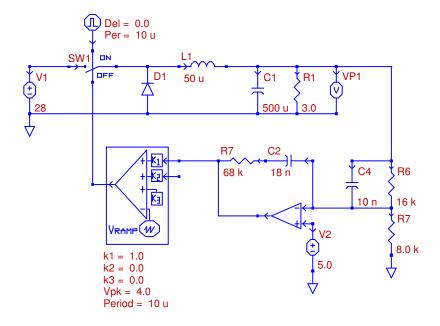

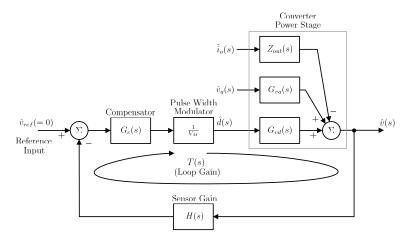

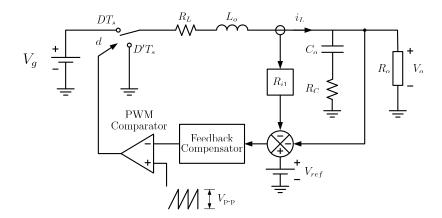

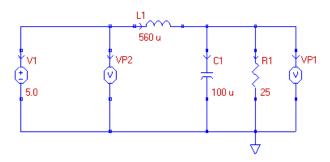

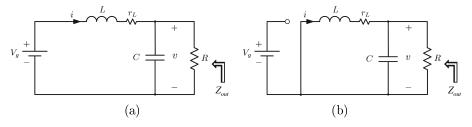

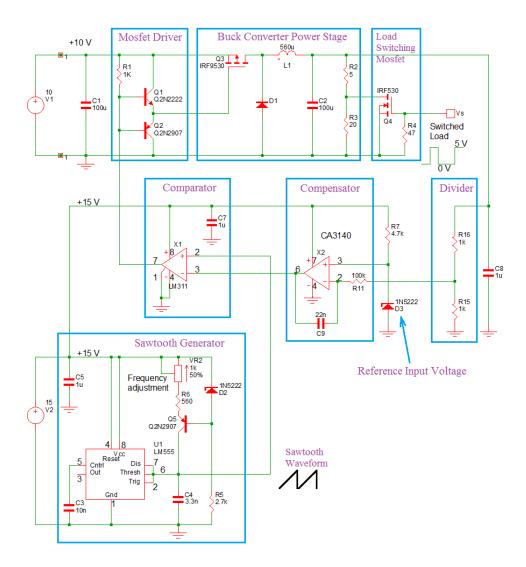

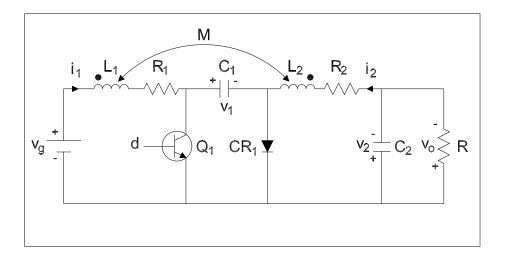

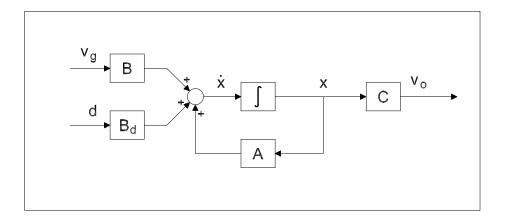

| 7 | 7.1  | v                                                          | 113 |

|   | –    | Introduction                                               |     |

|   | 7.2  | 7.2.1 Introduction                                         |     |

|   |      | 7.2.1 Introduction                                         |     |

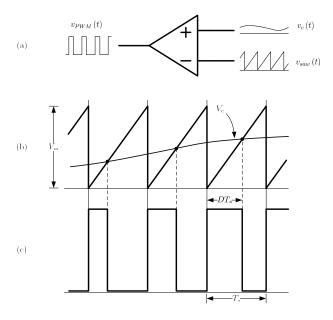

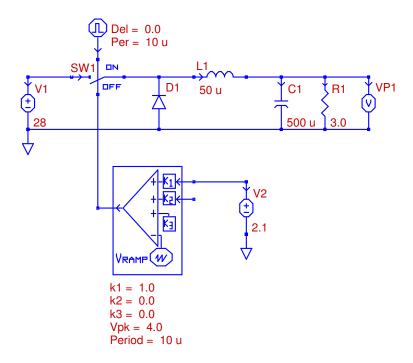

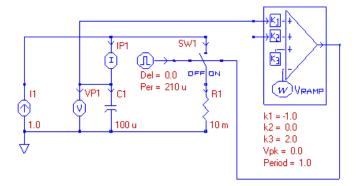

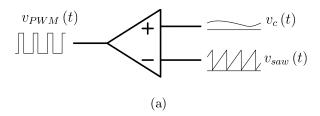

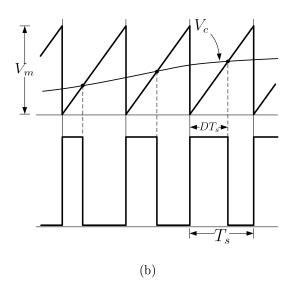

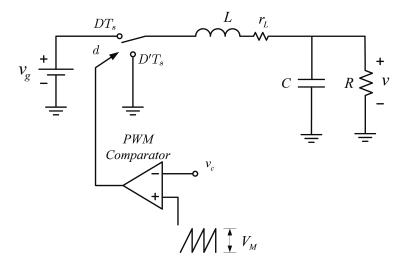

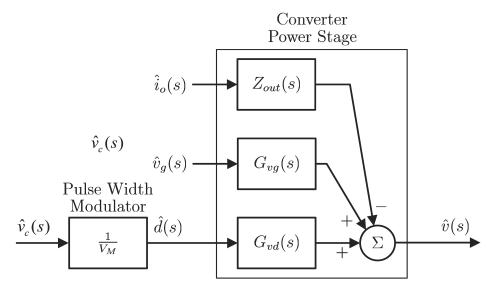

|   | 7.3  | Pulse-width Modulator                                      |     |

|   | 7.3  | Summary                                                    |     |

|   | 1.4  | Summary                                                    | 120 |

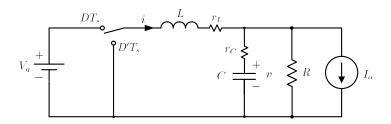

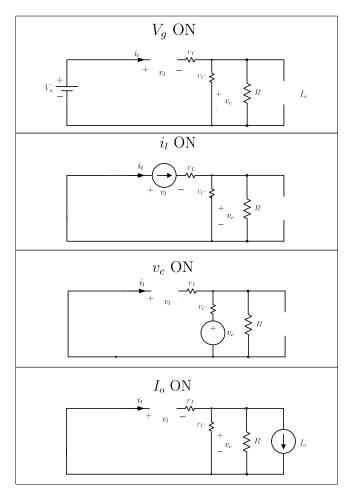

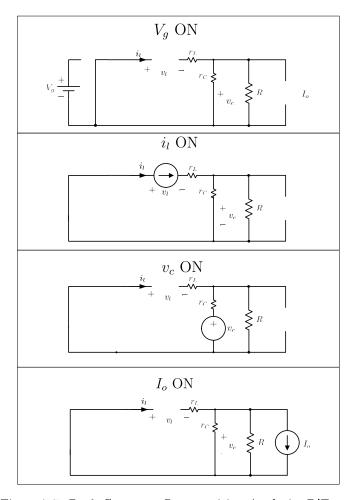

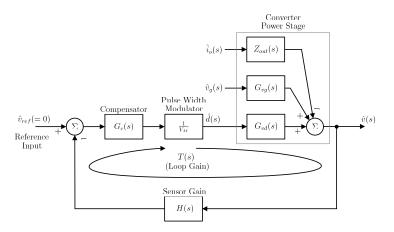

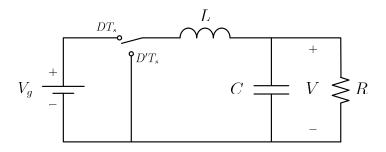

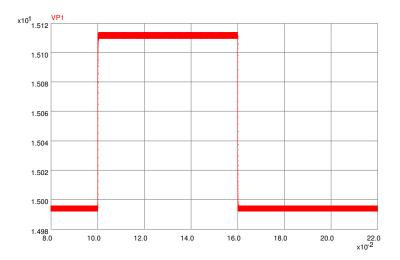

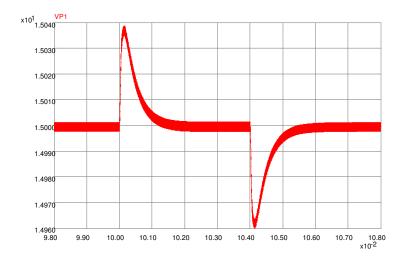

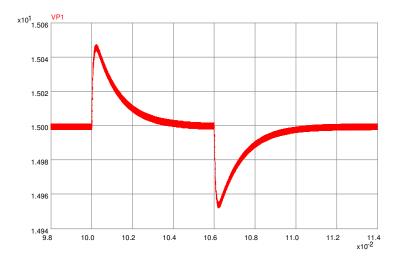

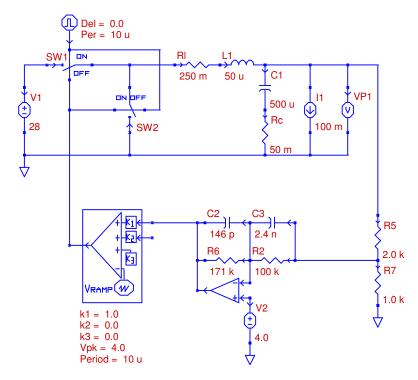

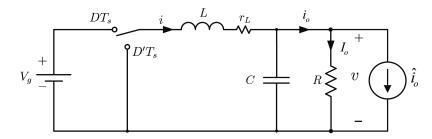

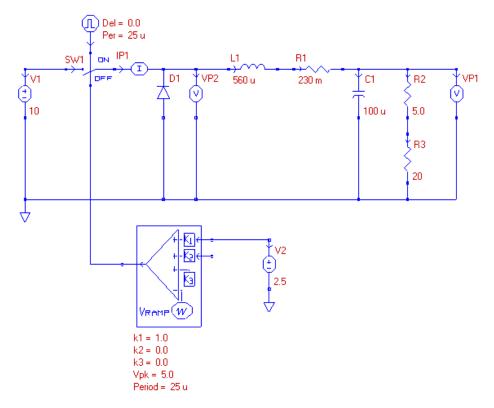

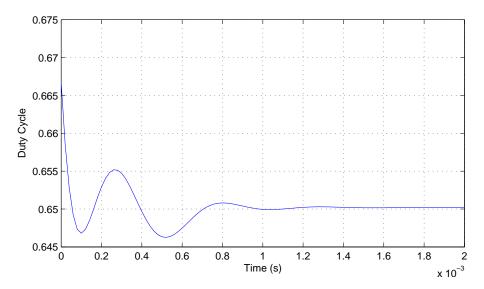

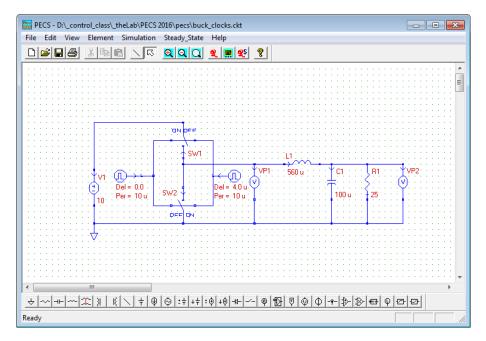

| 8 | Sing | 5 1 6                                                      | 127 |

|   | 8.1  | Introduction                                               |     |

|   | 8.2  | ů.                                                         | 128 |

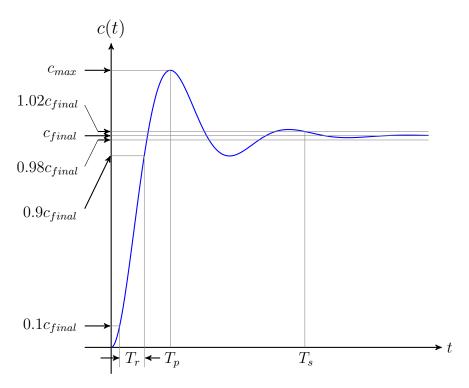

|   |      |                                                            | 128 |

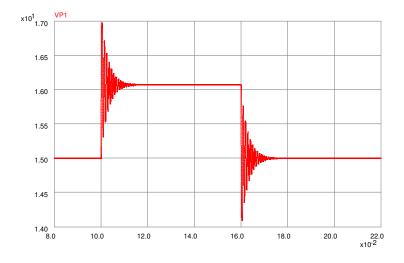

|   |      | ± v                                                        | 128 |

|   |      | 8.2.3 Design Targets                                       | 129 |

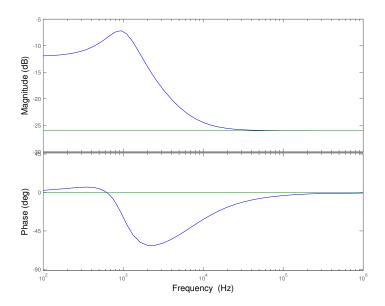

|          |                                           | 8.2.4 Buck Converter Model Analysis                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

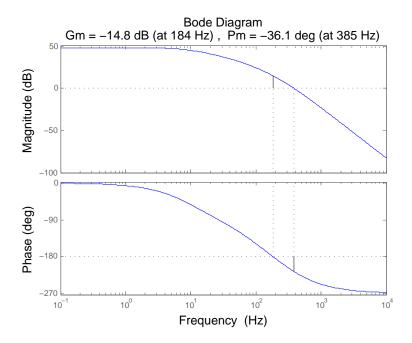

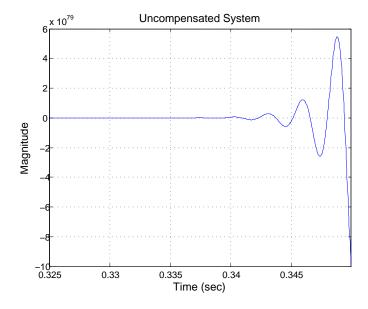

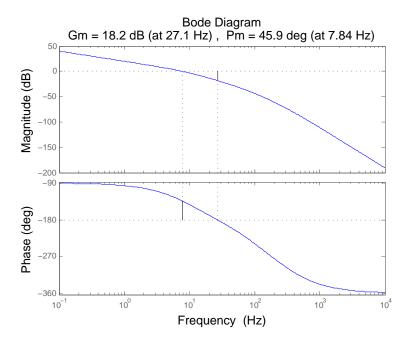

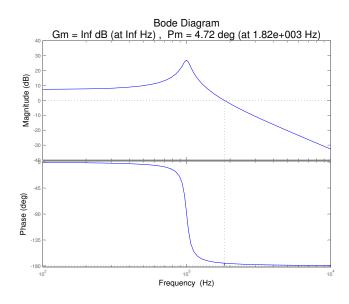

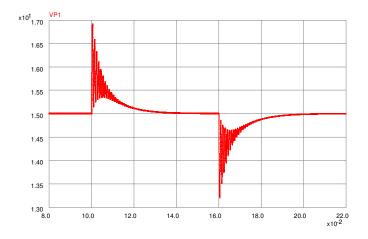

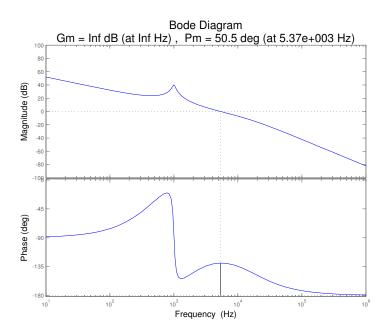

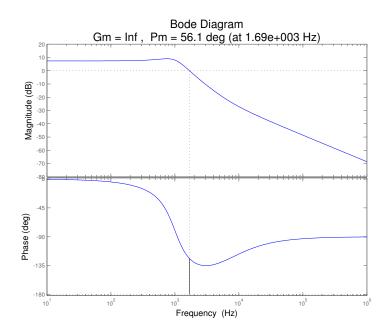

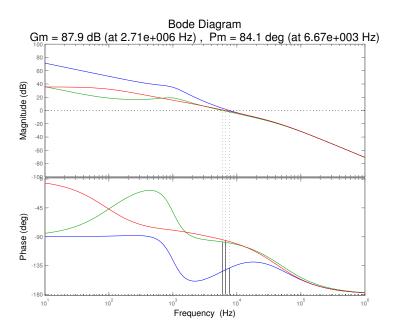

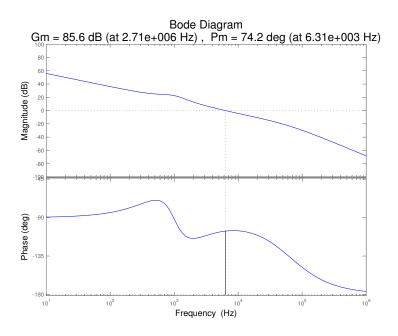

|          | 8.3                                       | Uncompensated System                                                                                                                                                                                                                                                                                                                                                                                                                                              |

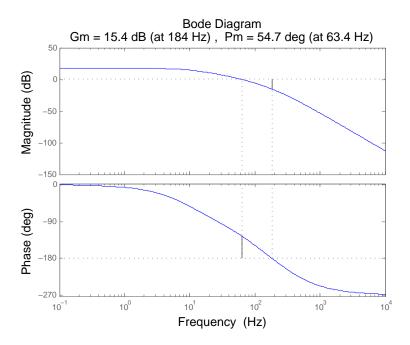

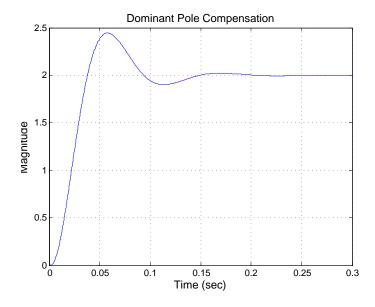

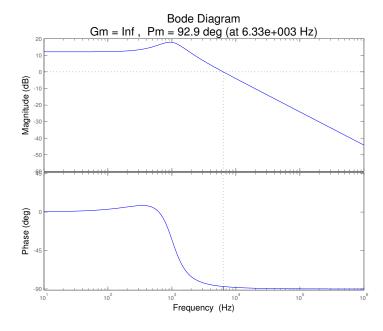

|          | 8.4                                       | Dominant Pole Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                        |

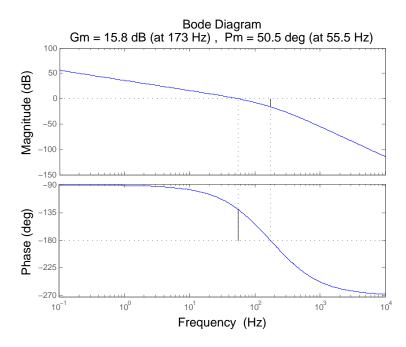

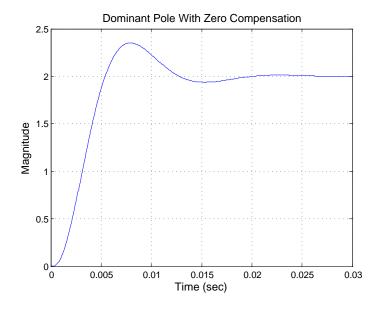

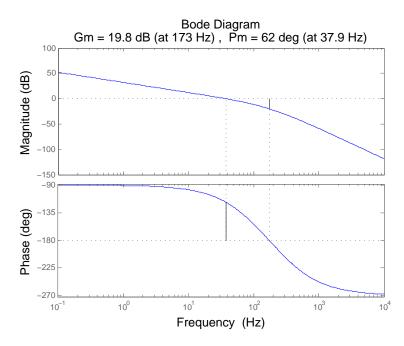

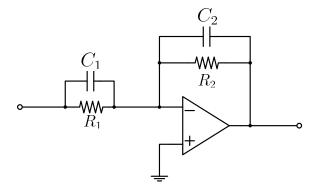

|          | 8.5                                       | Dominant Pole Compensation with Zero                                                                                                                                                                                                                                                                                                                                                                                                                              |

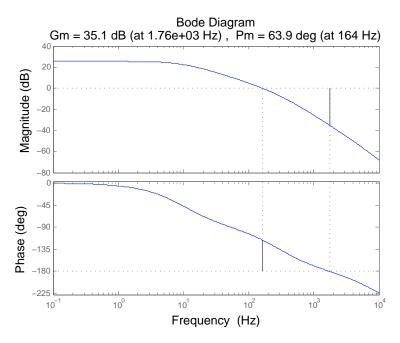

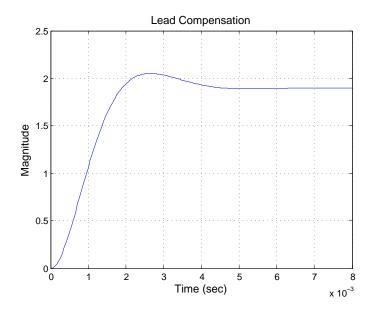

|          | 8.6                                       | Lead Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

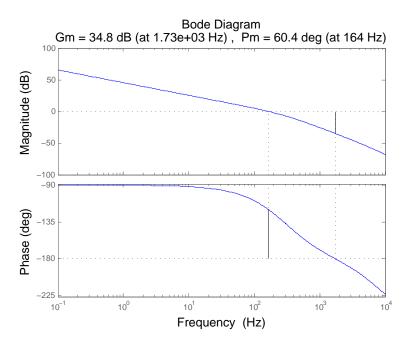

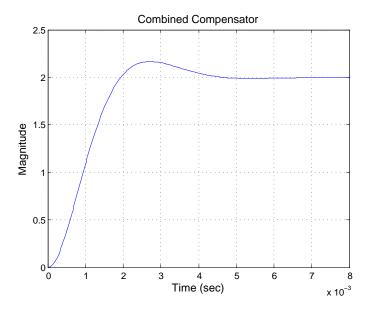

|          | 8.7                                       | Dominant Pole with Lead Compensation                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | O.,                                       | 8.7.1 Design 1: Zero $f_1 = 500$ Hz                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                                           | 8.7.2 Design 2: Zero $f_1 = 150 \text{ Hz}$                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 8.8                                       | Extended Bandwidth Design                                                                                                                                                                                                                                                                                                                                                                                                                                         |

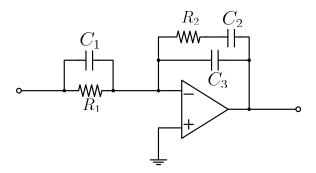

|          | 8.9                                       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

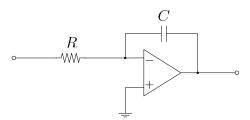

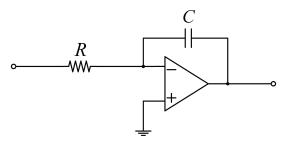

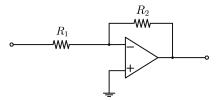

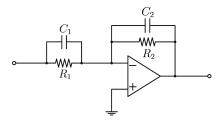

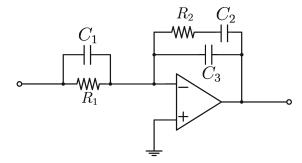

|          | 0.0                                       | 8.9.1 Compensator Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 8 1 N                                     | MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 0.10                                      | WATEAD Code                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

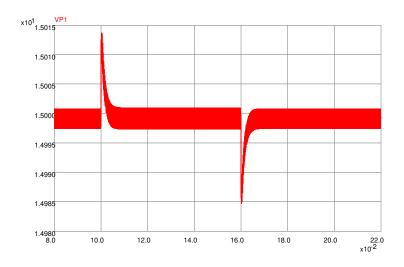

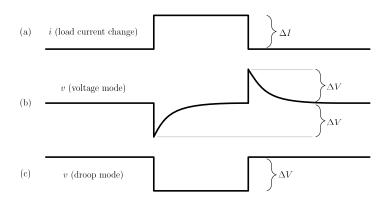

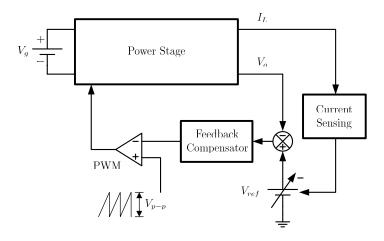

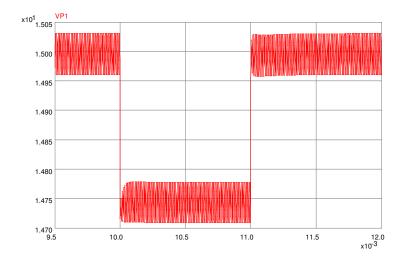

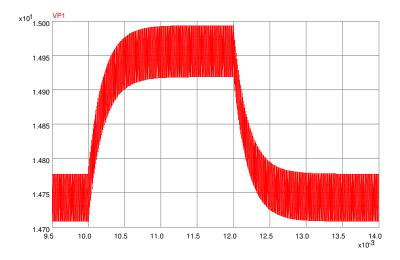

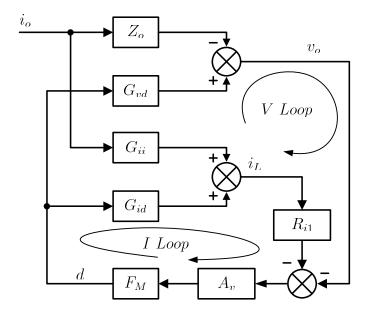

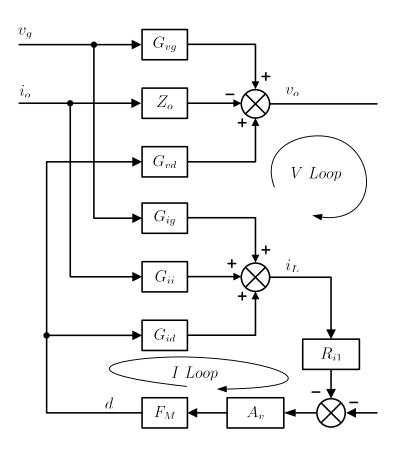

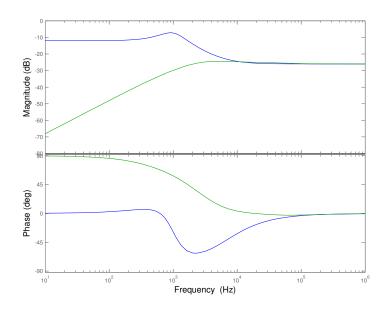

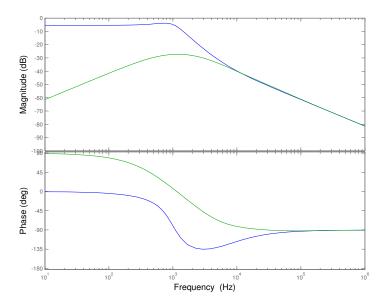

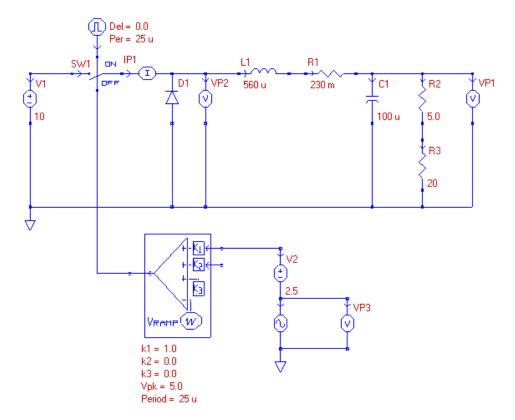

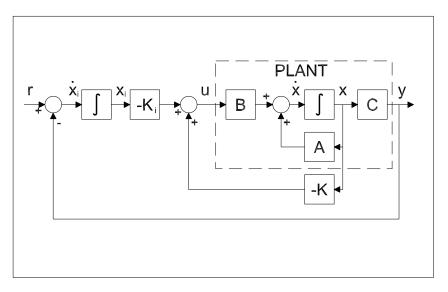

| 9        | Dro                                       | op and Multi-Loop Control 17                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 9.1                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 9.2                                       | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |                                           | 9.2.1 Passive Droop Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                                           | 9.2.2 Active Droop Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                                           | 9.2.3 Voltage Mode Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 9.3                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | 9.4                                       | MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 9.4                                       | MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 9.4                                       | MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TT       |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| II       |                                           | Classical Control: Laboratory 21                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | Ι (                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10       | I (                                       | Classical Control: Laboratory 213 oduction to the Labs 213                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10       | I () Intr                                 | Classical Control: Laboratory 213 oduction to the Labs 213                                                                                                                                                                                                                                                                                                                                                                                                        |